컴퓨터 구조와 논리회로

중간고사 대비 조합 논리회로와 순차 논리회로 개념 정리

KDY

2022. 10. 24. 19:28

728x90

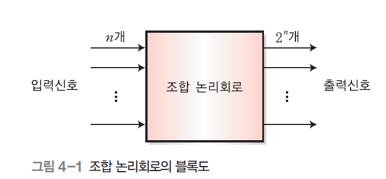

조합 논리회로 : 출력 신호가 입력 신호에 의해서만 결정된다.

- 종류 : 가산기, 비교기, 디코더와 인코더, 멀티플렉서와 디멀티플렉서, 코드 변환기 등이 있다.

순차 논리회로

- 출력 신호가 입력 신호뿐만 아니라 이전 상태의 논리 값에 의해 결정된다.

- 동기식 : 순차 논리회로는 클록 펄스가 들어오는 시점에 상태가 변화한다.

- 비동기식 : 순차 논리회로는 클록 펄스의 영향을 받지 않고 현재 입력되는 입력값이 변화하는 순서에 따라 동작한다.

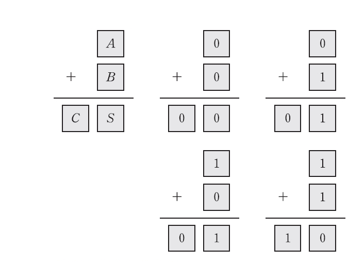

가산기

- 2개 이상의 입력을 이용하여 그 합을 출력하는 조합 논리회로

- 종류 : 반가산기, 전가산기

- 반가산기 : 1비트인 입력 2개와 출력 2개의 합(S)과 자리 올림수(C)가 사용 됨

| A | B | 올림수(C) | 합(S) |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

- 반가산기 : 반가산기의 진리표와 카르노맵을 이용하여 올림수와 합에 대한 최적으로 간략화된

불 대수식을 얻을 수 있다.

| A B-> | 0 | 1 |

| 0 | ||

| 1 | 1 |

(a) 자리 올림

| A B-> | 0 | 1 |

| 0 | 1 | |

| 1 | 1 |

(b) 합

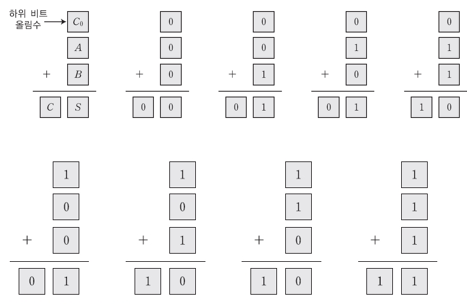

- 전가산기 : 2진수 3개, 즉 입력 A, B와 하위 비트에서 발생한 자리 올림수를 덧셈 연산하는 조합 논리회로다.

| A | B | C_0 | 올림수(C) | 합(S) |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

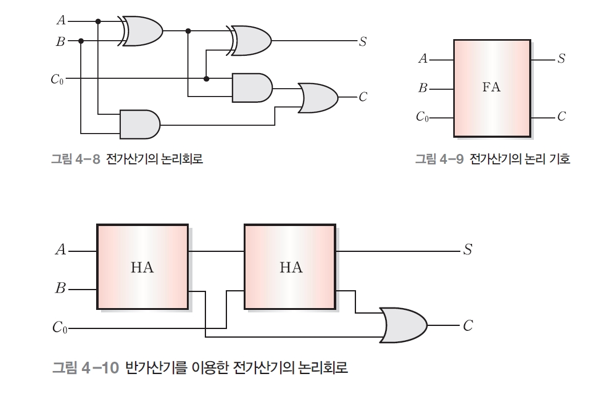

- 아래의 사진은 전가신기의 논리회로와 반가산기를 이용한 전가산기의 논리회로다.

- 병렬 가산기 : 전가산기를 병렬로 연결하면 여러 비트로 이뤄진 2진수의 덧셈 연산을 수행할 수 있다.

최하위 비트의 덧셈에서 발생하는 자리 올림수는 C_1, 그 다음 비트의 덧셈에서 발생하는 자리 올림수는 C_2이고 - 상위 비트에서 자리 올림수는 C_3와 C_4이다.

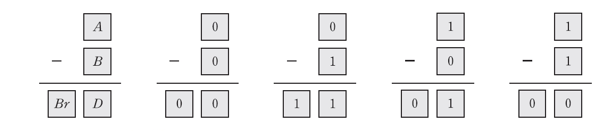

감산기

- 반감산기 : 1비트인 입력 2개와 출력 2개의 차(D)와 빌림수(Br)가 사용된다.

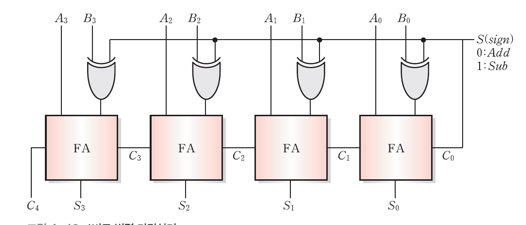

- 병렬 가감산기 : 디지털 장치에서 별도로 감산기를 사용하지 않고 가산기에 게이트를 추가해 부호 선택 신호로 뺄셈 연산을 수행

-> 4비트 병렬 가산기의 입력 B에 XOR 게이트를 추가해 만든 병렬 가감산기.

-> XOR 게이트에 입력되는 부호 선택 신호의 값이 0이면 덧셈 연산을 수행

-> 부호 선택 신호의 값이 1이면 뺄셈 연산을 수행

인코더와 디코더

- 인코딩 : 정보의 형태와 형식의 표준화, 보안, 처리 속도 향상, 저장 공간 절약 등을 목적으로

다른 형태나 형식으로 변환하는 처리 또는 처리 방식으로 부호화라고 한다. - 디코딩 : 인코딩된 정보를 인코딩되기 전으로 되돌리는 처리 또는 처리 방식으로 복호화라고도 한다.

- 인코더 : 외부에서 들어오는 임의의 신호를 부호화된 신호로 변환하여 컴퓨터 내부로 들여보내는 조합 논리회로다.

8 x 3 인코더는 8비트의 입력 D 중에서 활성화된 값 1의 위치에 따라 3비트의 출력을 얻는 장치이다.

| D_7 | D_6 | D_5 | D_4 | D_3 | D_2 | D_1 | D_0 | C | B |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

| 00 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

표로 만들려고 했으나 짤리는 관계로

멀티 플렉서와 디멀티플렉서

- 멀티플렉서는 여러 개의 입력 중 하나만 출력에 전달하는 조합 논리회로다.

- 디멀티플렉서는 한꺼번에 들어온 여러 신호 중 하나를 골라 출력한다.

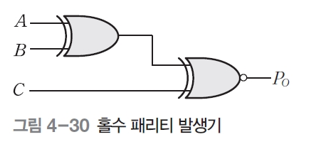

패리티 검사기

- 짝수 패리티 발생기 : 패리티 비트 발생기의 진리표에서 짝수 패리티 비트를 참고해 불대수식으로 나타내면

P_E=A⊕B⊕C이고

- 홀수 패리티 발생기 : 홀수 패리티 비트를 참고해 불 대수식으로 나타내면P_0=¯(A⊕B⊕C)

레지스터 대표적인 순차논리회로

- 데이터를 좌우로 이동하는 레지스터를 이동 레지스터라고 한다.

- 직렬 입력-병렬 출력, 병렬 입력-직렬 출력 행태가 포함된 직렬과 병렬의 입출력 조합을 가지고 있다.

- 병렬 입력-직렬 출력 이동 레지스터 : 각 플릭플롭에 입력되는 데이터 연산 I 4개, 데이터 이동 레지스터 안에 병렬로 들어가게 하는 SHIFT / ̅(LOAD)입력이 있다.

- SHIFT / ̅(LOAD)입력이 0이면 AND 게이트 G_1 ~ G_3에 입력되는 I가 각 플립플롭의 새로운 입력으로 가해지고, 클록 펄스가 발생하면 각 단의 플립플롭에서 출력된다. ( LOAD는 0일 때, SHIFT는 1일 때)

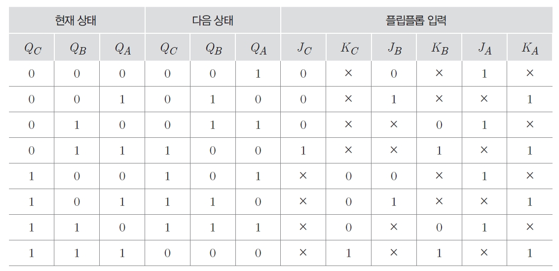

카운터(Counter, 계수기)

- 상향 비동기식 카운터 : 4비트 2진 상향 카운터는 0부터 클록의 수가 증가하면 계수의 값이 증가해 15까지 되고 클록에 의해 0으로 돌아간다.

- 3비트 동기식 2진 카운터 : 8개의 순차적인 상태(000, 001, 010, 011, 100, 101, 110, 111)를 가진다.

- 링 카운터 : 첫 번째 플립플롭의 출력이 두 번째 플립플롭으로, 두 번째 플립플롭의 출력이 세 번째 플립플롭으로 연결되고, 최종 플립플롭의 출력이 첫 번째 플립플롭으로 되돌아가도록 연결된다.